### A Translator Verification Technique for FPGA Software Development in Nuclear Power Plants

<u>Jaeyeob Kim</u>, Eui-Sub Kim, Junbeom Yoo

Konkuk University

#### Outline

- 1. Introduction

- 2. Background

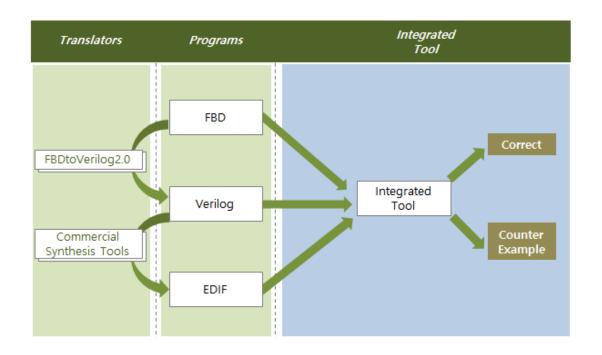

- 3. The Integrated Tool for Demonstrating the Correctness of Translator

- 1. Overall Process

- 2. Input programs

- 3. Scenario Generation

- 4. Simulation & Comparison

- 4. Case Study

- 5. Conclusion & future work

### Introduction (1/2)

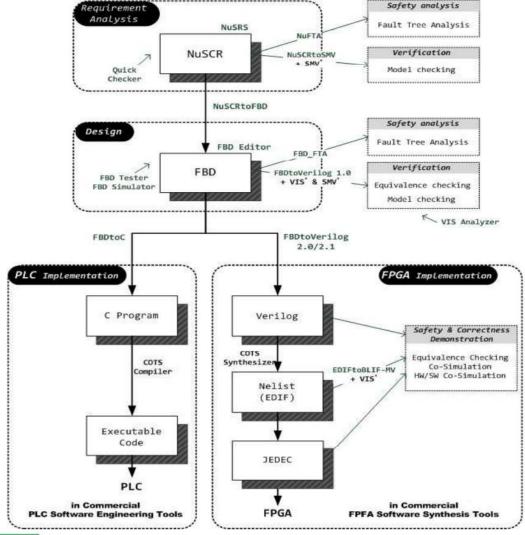

#### **NuDE 2.0**

### Introduction (2/2)

#### Verifying 'FBDtoVerilog'

- Co-Simulation technique can be used for demonstrating the correctness of translator such as 'FBDtoVerilog'

- For this co-simulation technique, many tools run separately such as 'Scenario Generator', 'FBD Simulator'

- We had develop integrated tool to support the co-simulation

### Background(1/3)

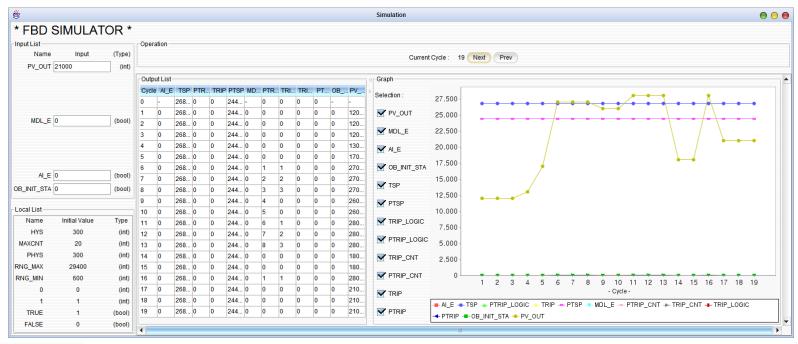

#### **FBD Simulator**

- Simulator for FBD

- Automatically classifies the POU (Program of Unit) in the FBD

- It presents input, output and local variable lists

### Background(2/3)

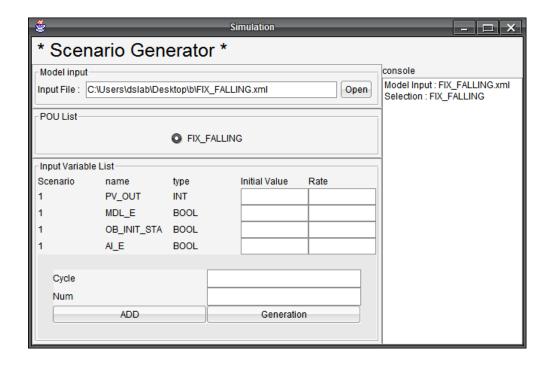

#### **Scenario Generator**

- A tool that automatically generate an infinite number of scenarios

- Input is FBD

- It reflects the features of the domain such as range of value

### Background(3/3)

#### **Co-Simulation**

- Indirect verification technique

- It simulates programs with same scenario and compares results of simulation for confirming correctness

- Confirmation of correctness with co-simulation can make to enhance the <u>reliability</u> of the program

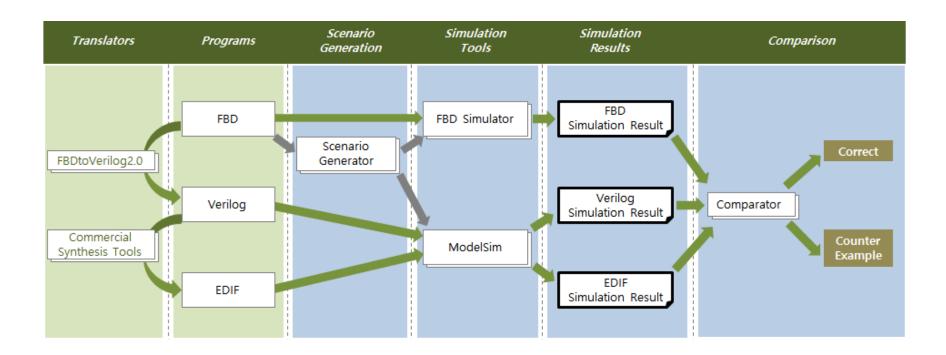

#### **Overall Process – Before Using Integrated Tool**

#### **Overall Process – Using Integrated Tool**

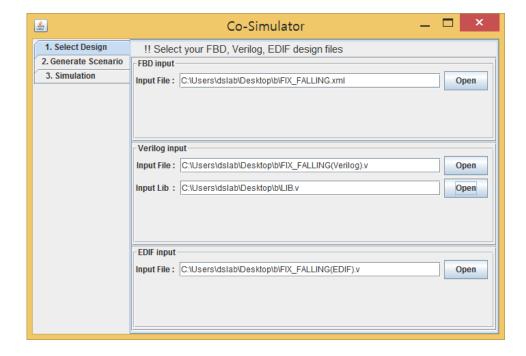

#### **Input programs**

- FBD

- Verilog

- EDIF

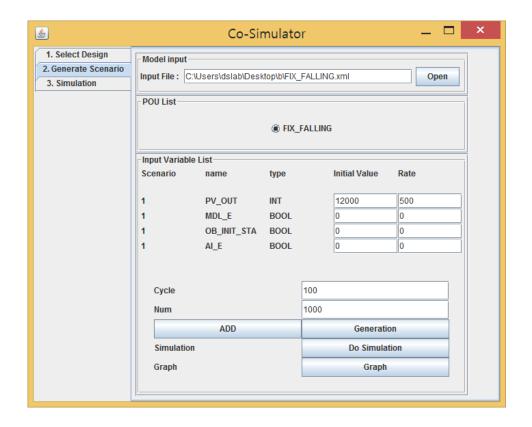

#### **Scenario Generation**

- Use 'Scenario Generator'

- Create script (.do file)

for automatically use of

ModelSim

ModelSim Script (.do file)

```

quietly set ACTELLIBNAME proasic3e

if {[file exists presynth/ info]} {

echo "INFO: Simulation library presynth already exists"

} else {

file delete -force presynth

vlib presynth

ymap presynth presynth

vmap proasic3e "C:/Microsemi/Libero v11.4/Designer/lib/modelsim/precompiled/vlog/proasic3e"

vlog -work presynth "C:/Users/dslab/Desktop/myfile.v"

vlog -work presynth "C:/Users/dslab/Desktop/test 1001/hdl/LIB.v"

Viog "+incolr+c:/users/gs.ap/pesktop/result" -work presyntn "c:/users/gs.ap/pesktop/result/verliog_Test_benchs_for_scenario_scenario_1/scenario_1_0.v

vsim -L proasic3e -L presynth -t 1ps presynth.scenario_1_0

add wave /scenario 1 0/*

run 1000us

add list -decimal *

write list C:/Users/dslab/Desktop/result/scenario 1 0 verilog.lst

Viog "+incair+C:/Users/gsiab/Desktop/resuit" -work presynth "C:/Users/gsiab/Desktop/resuit/Verilog Test Benchs for scenario/scenario 1/scenario 1/scenario

vsim -L proasic3e -L presynth -t 1ps presynth.scenario_1_1

add wave /scenario 1 1/*

run 1000us

add list -decimal *

write list C:/Users/dslab/Desktop/result/scenario 1 1 verilog.lst

```

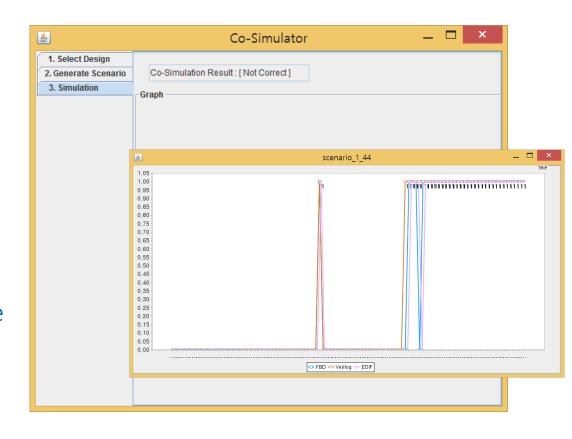

#### **Simulation & Comparison**

- Simulation

- Comparison

- Result

- Correct

- Not Correct

- → Counter example

Simulation result file

| Name be |       |       |       |     |       |      |         |      |        |            |       |

|---------|-------|-------|-------|-----|-------|------|---------|------|--------|------------|-------|

| scenari | 0_1_  | _1    |       |     |       |      |         |      |        |            |       |

| end     |       |       |       |     |       |      |         |      |        |            |       |

|         |       |       |       |     |       |      |         |      |        |            |       |

| Outputs | beg   | gin   |       |     |       |      |         |      |        |            |       |

| TSP PTF | RIP_I | LOGIC | TRIP  | PTS | 3P    | PTI  | RIP_CNT | TRI  | P_CNT  | TRIP_LOGIC | PTRIP |

| end     |       |       |       |     |       |      |         |      |        |            |       |

| Feedbac | ·k he | arin  |       |     |       |      |         |      |        |            |       |

|         |       | -     | PTSP  | pmi | RTP ( | יותי | TRIP CN | ייינ | TRIP L | OGTC       |       |

| end     |       | 20010 |       |     |       |      |         | •    |        |            |       |

|         |       |       |       |     |       |      |         |      |        |            |       |

| Result  | begi  | in    |       |     |       |      |         |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 1   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 2   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 3   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 4   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 5   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 6   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 7   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 8   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 0   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 0   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 0   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 0   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 1   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 2   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 3   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 4   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 5   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 6   | 0     | 0    | 0       |      |        |            |       |

| 26805   | 0     | 0     | 24429 | 7   | 0     | 0    | 0       |      |        |            |       |

| ps      |     | /scenario_1_0/SYSCLK  | /   | sc | enario_ | 1_0 | /AI_E      | /scena | ario_1_ | 0/PTSP  | /s  | cenario_1_0/ | /TR | IP |    |

|---------|-----|-----------------------|-----|----|---------|-----|------------|--------|---------|---------|-----|--------------|-----|----|----|

| de      | lta | /scenario_1_0/NSYSRES | EТ  | /  | scenari | 0_1 | _0/OB_INIT | STA    | /scen   | ario_1_ | 0/1 | RIP_CNT      |     |    |    |

|         |     | /scenario_1_0/p       | ıls | e  |         |     | /scena     | rio_1  | 0/TSP   | /scena  | ric | _1_0/PTRIP_0 | CNT |    |    |

|         |     | /scenario             | 1_  | 0/ | PV_OUT  |     | /sce       | nario_ | 1_0/TR  | IP_LOGI | C   | /scenario_1_ | _0/ | PT | RI |

|         |     | /scena                | rio | _1 | _0/MDL_ | E   | /30        | enario | _1_0/P  | TRIP_LO | GIC | :            |     |    |    |

| 0       | +0  | 0                     | 0   | 0  | 26000   | 0   | 0          | 0      | x       | x       | x x | x x          | ×   | ×  | 1  |

| 50000   | +0  | -1                    | 0   | 0  | 26000   | 0   | 0          | 0      | x       | x       | x x | x x          | ×   | ×  | :  |

| 100000  | +0  | 0                     | 0   | 0  | 26000   | 0   | 0          | 0      | x       | ×       | x x | x x          | ×   | ×  |    |

| 150000  | +0  | -1                    | 0   | 0  | 26000   | 0   | 0          | 0      | x       | x       | x x | x x          | ×   | ×  |    |

| 200000  | +0  | 0                     | 0   | 0  | 26000   | 0   | 0          | 0      | x       | x       | x x | x x          | ×   | ×  |    |

| 250000  | +0  | -1                    | 0   | 0  | 26000   | 0   | 0          | 0      | x       | x       | x x | x x          | ×   | ×  |    |

| 300000  | +0  | 0                     | 0   | 0  | 26000   | 0   | 0          | 0      | ×       | x       | x x | x x          | ×   | ×  |    |

| 350000  | +0  | -1                    | 0   | 0  | 26000   | 0   | 0          | 0      | ×       | x       | K 3 | x x          | х   | ×  |    |

| 400000  | +0  | 0                     | 0   | 0  | 26000   |     | 0          | 0      | ×       | ×       | х э | x x          | ×   | ×  |    |

| 450000  | +0  | -1                    | 0   | 0  | 26000   | 0   | 0          | 0      | ×       | ×       | x x | x x          | ×   | ×  |    |

| 500000  | +0  | 0                     | 0   | 0  | 26000   | 0   | 0          | 0      | ×       | x       | x x | x x          | ×   | ×  |    |

| 550000  | +0  | -1                    | 0   | 0  | 26000   | 0   | 0          | 0      | x       | x       | K 3 | x x          | х   | ×  |    |

| 600000  | +0  | 0                     | 0   | 0  | 26000   | 0   | 0          | 0      | ×       | x       | x x | x x          | ×   | ×  |    |

| 650000  | +0  | -1                    | 0   | 0  | 26000   | 0   | 0          | 0      | ×       | x       | x x | x x          | ×   | ×  |    |

| 700000  | +0  | 0                     | 0   | 0  | 26000   | 0   | 0          | 0      | ×       | x       | K 3 | x x          | х   | ×  |    |

| 750000  | +0  | -1                    | 0   | 0  | 26000   | 0   | 0          | 0      | x       | x       | х э | x x          | ×   | ×  |    |

| 800000  | +0  | _                     |     | 0  | 26000   | _   | 0          | 0      | ×       | ×       | x x | x x          | ×   | ×  |    |

| 850000  | +0  | -1                    |     | 0  | 26000   |     | 0          | 0      | ×       | ×       | x x | x x          | ×   | ×  |    |

| 900000  | +0  |                       | -   | 0  | 26000   |     | 0          | 0      | ×       | x       | к э | x x          | х   | ×  |    |

| 950000  | +0  | -1                    | -   | 0  | 26000   | _   | 0          | 0      | x       | ×       | x > | x x          | ×   | ×  |    |

| 1000000 | +0  | -1                    | *   | 0  | 26000   | _   | 0          | 0      | ×       | ×       | x x | x x          | ×   | ×  |    |

| 1000000 | +1  | 0                     | *   | 0  | 26000   |     | 0          | 0      | ×       | x       |     |              |     | ×  |    |

| 1000300 | +0  | 0                     | *   | 0  | 26000   | 0   | 0          | 0      | 26805   | 24429   | 0 0 | 0            | 0   | 0  |    |

| 1050000 | +0  | -1                    | *   | 0  | 26000   | 0   | 0          | 0      | 26805   | 24429   | 0 0 | 0            | 0   | 0  |    |

| 1100000 | +0  | 0                     | *   | 0  | 26000   | 0   | 0          | 0      | 26805   | 24429   | 0 0 | 0            | 0   | 0  |    |

<FBD Simulation result>

<ModelSim Simulation result>

### Case Study

KNICS RPS BP

|                   | FIX_FALLING | FIX_RISING | MANUAL_RATE_<br>FALLING | VARIABLE_<br>FALLING | VARIABLE_<br>RISING |

|-------------------|-------------|------------|-------------------------|----------------------|---------------------|

| Scenario          | 1000        | 1000       | 1000                    | 1000                 | 1000                |

| Initial<br>Values | 12000       | 26000      | 15000                   | 15000                | 15000               |

| Rate of<br>Change | 500         | 500        | 500                     | 100                  | 100                 |

| Cycles            | 100         | 100        | 100                     | 100                  | 100                 |

| Time              | 57:07       | 56:50      | 1:08:13                 | 59:03                | 58:56               |

#### **Total 5000 scenario / All Correct**

#### Conclusion and future work

- We developed the integrated tool in order to automatically perform the co-simulation

- We demonstrated the correctness of translator

- 'FBDtoVerilog2.0'

- 'Synplify Pro'

- We plan to extend the integrated tool to verify VHDL

- And plan to elaborate the scenarios on the basis of adequate coverage criteria in order to increase the confidence of verification

### THANK YOU